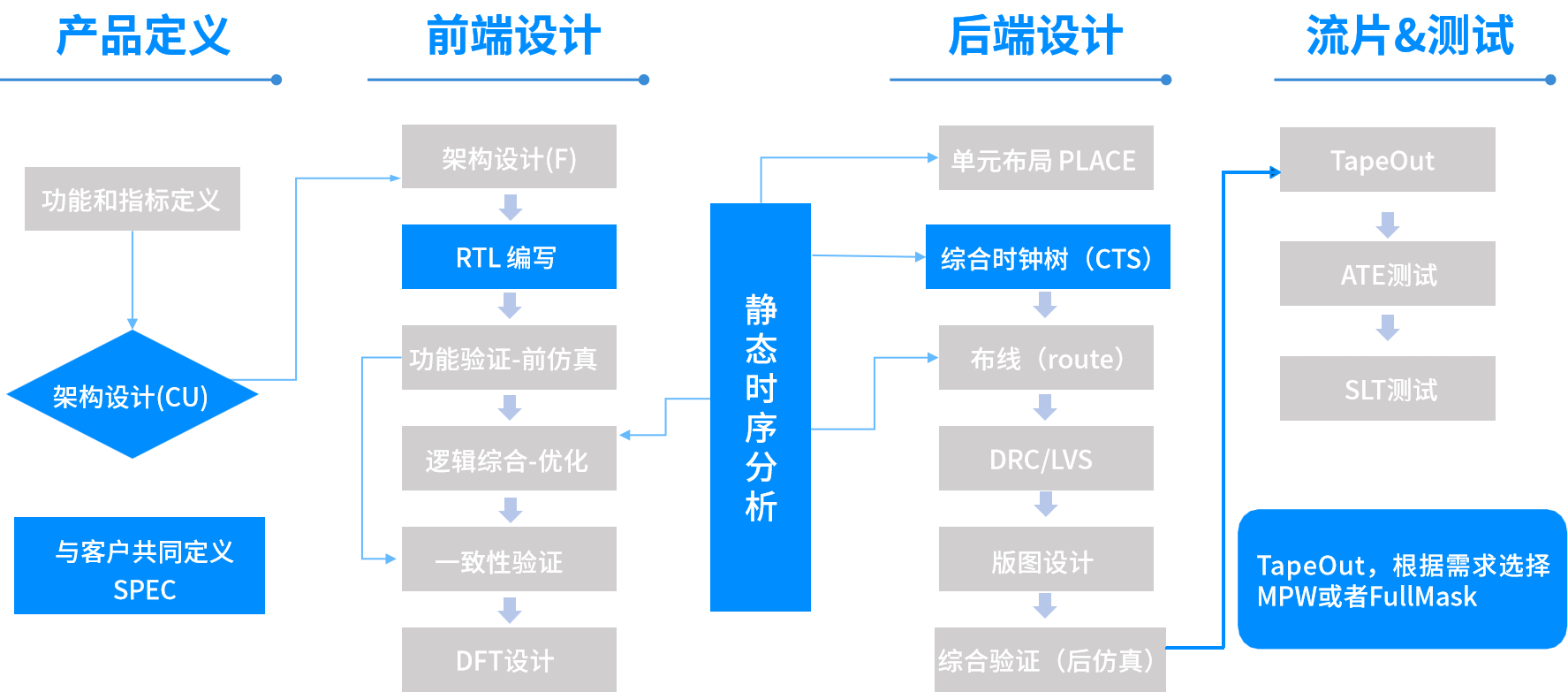

叩持电子提供的SoC设计服务涵盖了0.5um到先进的5nm/4nm/3nm等工艺节点制程,包括各种产品形态的芯片设计实现,完善的流程方法可以解决实现几十亿门级以上的规模设计、GHz工作频率、深亚微米噪声耦合、IR压降、静电(ESD)放电、可制造性设计(DFM)、良率设计提升(DFY)与严峻上市时程需求的挑战。

除了结构化设计流程实现分析、时钟树合成、芯片及工艺变化(OCV)的静态时序分析、功能验证、多重电源领域并考虑各自开与关的验证、串扰(cross-talk)修整与预防及先进工艺下的物理验证(Physical Verifications)外,叩持电子的先进设计流程,增加了快速原型制作、自动化电源设计方案(考虑压降与可绕性的电源铺设,依照电流量与电压爬升率的电源开关并串接, 防范动态压降的电源密度分析),有效减少时序收敛的设计流程迭代(针对不同温度/电压/制成的定制化方案sign off, 数据流分析工具, 时钟延迟CDA单元库定制,hold-free工艺库定制等),可制造性设计,及良率设计等已经通过数百个在深亚微米技术上第一次设计就成功的芯片设计客户项目的考验。

另一方面,叩持电子也提供完备严谨的可测试性设计(design-for-testability,DFT)服务,包括扫瞄电路合成(scan insertion)、边界扫描(Boundary Scan Insertion, 1149.1/1149.6)、智能分组内存BIST测试、扫描重新链接(scan re-ordering)基于后端绕线资源及性能影响、低耗电测试图样产生与高速运算 DFT服务。此外,Coachip叩持电子还提供IP定制实现,IP设计集成及测试集成, SoC设计服务,涵盖从产品规格定义到GDSII (Specin2GDSII)或从RTL到GDSII (R2GDSII)。多年来叩持电子已经成功设计实现了不同产品形态错综复杂的SoC,为数百个客户项目成功量产。

以上所有解决方案皆整合与嵌入于叩持电子工作流程管理系统(WFM),已达成在极佳效率下坚持不妥协的产品质量。